头图|CSDN下载自东方IC

出品|CSDN(ID:CSDNnews)以下为译文:

![图片[1]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_0.jpg)

现代的大型电子产品常常基于某个高度集成的芯片打造,这些芯片称为“系统芯片”(SystemonaChip,简写:SoC)。最早的家用计算机显卡大概包含一百多个芯片,但是当80286PC/AT兼容机成为主流后,在摩尔定理的促进下,显卡上的芯片降低到了寥寥几个,但是这个行业永远不会走回头路。如今,典型的SoC可以集成一个CPU核心组件,以及数十个外围设备,包括模拟、RF和电源等功能。我们甚至还有“系统级封装”解决方案,可将SoC、RAM,有时甚至将FLASH芯片封装到一个塑封中。

现代SoC十分复杂。现代SoC完整的“用户指南”往往历时几千页,而bug列表也有几百页。我在“用户指南”上加了顿号,由于虽然是最开放、文档最齐全的SoC(比如NXP的i.MX系列),也必须签订严格的保密合同,能够阅读各类第三方知识产权功能模块对应的数千页文档,比如视频解码、图形加速以及安全等。不仅须要保密合同的文档之外开源操作系统有哪些,一般还有数千页未发布的、针对这些不再使用的芯片区域的文档,比如原先设计中包含但最终无法成功的外围设备,内部调试工具以及预引导工具等。许多不再使用的功能,甚至连设计芯片的团队都不晓得!

不再使用的芯片区域是一件大事,由于建立芯片可不像搭乐高积木那般简单,它更像是精雕家刻在花岗岩快上的石雕,因而添加电路的难度远远低于关掉电路。降低一条电路仅制做新的掩膜就大概须要耗费100万美金,同时就会造成项目延后70天(大概10千人时的额外工作)。而在正确计划的情况下,关掉一条电路十分简单,只须要更改代码,或则针对某个掩模层进行轻微改动,只须要耗费大概1万欧元以及几天的延后(假定晶片尚处于中期阶段,很容易进行这样的改动)。

![图片[2]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_1.jpg)

为此,刚开始的时侯,系统芯片的掩模组往往拥有好多额外的功能、备用逻辑和调试功能,之后逐渐剔除(弃用)部份功能,直至最后系统芯片成形。正如米开朗基罗以前说:“每一块花岗岩中都隐藏着一个雕塑,而雕像家的任务就是发觉它。”而我们可以说:“每个系统芯片的掩模组中都隐藏着一个数据指南,而验证团队的任务就是发觉它。”有时,最后的修复发生在启动时刻,借助一些在CPU执行任何指令之前就执行的代码来关掉错误的功能或则打补丁。这样做的结果就是,就算是文档最健全的系统芯片中,被标记为不再使用的晶体管数目也不可忽略,虽然理论上这种晶体管不会被用户听到。从安全角度来看,系统芯片中的这些“暗物质”的存在令人忧心。何必害怕ROM的启动或CPU微代码的问题,内建自测试(BuiltinSelfTest,即BIST)基础设施具有执行代码注入所需的一切,你只需将它设置为正确的模式。据悉,系统芯片集成商就会从寥寥几个IP供应商那儿订购DDR、PCI和USB等功能块。这意味着,成千上万的设备都加载了相同的弃用逻辑单元,甚至不同品牌和竞争产品之间也一样。所以,系统芯片中存在难以修复,甚至可能破坏生态系统的危险!为了规避这些风险,Precursor使用FPGA来实现系统芯片。FPGA容许使用者重新编程,因而极大地增加了设计错误带来的成本。我们何必再像石材精雕那样做加法,而是可以像乐高积木那样来搭建。其实,这些灵活性须要付出一定的代价:FPGA的价钱比同等功能的系统芯片高50倍,而绝对频度则慢5-10倍。并且,这样能保证Precursor中没有暗物质,由于描述系统芯片的每一行代码都可以查看。这也意味着,假如Precursor的系统芯片中发觉逻辑错误,则可以通过更新对其进行修复。这大大减少了迭代系统芯片的成本,从经济的角度来看它也可以向开源靠拢。理想情况下,Precursor的系统芯片设计将在未来几年内成熟并接受彻底的审查,以低风险的方法朝着塑造固定芯片的方向发展,进而减少生产成本并提升性能开源操作系统有哪些,同时保持高标准的透明度。

LiteX:Precursor系统芯片背后的框架Precursor的系统芯片使用LiteX建立。LiteX是由FlorentKermarrec创建的框架,使用Migen/MiSoCFHDL定义系统芯片,该框架本身是用Python3.6+编撰的。LiteX的核心是一组“处理程序”,它们就能手动按照总线标准和长度进行适配。这样,设计人员可以很容易地在Wishbone、AXI和CSR等总线互联标准下混和使用不同的控制器和外设。只需几行代码就可以将一个额外的USB调试控制器联接到一个复杂的系统芯片中,但是整个总线仲裁和适配器的构架就能自行作出响应。Precursor系统芯片简介

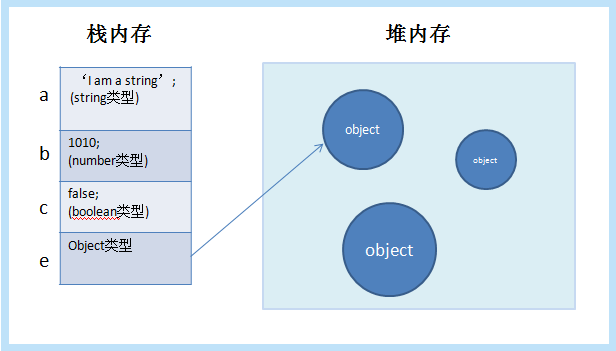

![图片[3]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_4.png)

上图是于2020年10月发表的Precursor芯片系统的示意图。请随时关注图中的日期,由于基于FPGA的系统芯片会不断发生变化。通常,我们都不用太在乎如此漂亮的手绘示意图,由于一般这种图片在完成的那三天就早已过时了。而我们的CI系统会在每次代码推送时,动态生成“程序员指南”。对于Rust程序员,我们的svd2utra工具可将LiteX生成的SVD文件手动转换为RustAPI的crate。使用基于FPGA的开源系统芯片,手动化CI除了是最佳实践,并且是至关重要的部份,由于有时子模块依赖项中一个很小但很重要的补丁会不断影响你的设计。

核心区域

“核心区域”(CoreComplex)目前由一个RISC-V核心构成,它由CharlesPapon的VexRiscV实现。我们将其配置为支持“RV32IMAC”指令子集,给它添加了一个MMU,还加强了缓存。VexRiscV将缓存大小限制为4kB,但可以通过减小缓存关联来增强有效容量。通过给核心添加一个单向I-cache和一个四向D-cache,我们将性能提高了大概10%。我们还打算了一个32kB的启动ROM,目前包含三条指令,但之后可以扩充,可以对从外部显存加载的代码进行签名检测。还有一个128kB的板载SRAM,用于紧密耦合或高安全性的操作。CPU核心被适配到一个由LiteX实现的Wishbone总线多用控制器上,之后可以进一步借助独立的CSR桥适配到CSR总线上,只须要将CSR桥配置为手动在4kB页面边界上进行空间并行,因而与MMU单独构建映射。还有一个IRQ控制器负责管理来自芯片周围外设的中断。

![图片[4]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_7.png)

核心区域还包含一组负责执行下边功能的CSR,大部份为样板代码:

调试块

核心区域后面是一个调试块。调试块拥有一个全速的USBMAC/PHY,负责为Wishbone包打开隧洞,从CPU的角度来看,它是另一个Wishbone控制器。我们使用给它来驱动CPU上的调试插口。这样虽然CPU停机,也可以通过USB用GDB联接到Precursor上。甚至可以建立一个不带RISC-VCPU的Precursor,之后通过USB来为Wishbone包打开隧洞,进行调试和驱动开发。调试块还包含一个名为“Messible”的大型CSR外设,这是一个包含64个元素的8主频FIFO,可以在调试时作为邮箱或草稿使用。

![图片[5]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_10.png)

显存映射和CSRI/O

RISC-VCPU的显存空间通过Wishbone总线映射到多种外设和显存块上。在传统的系统芯片设计师看来,Wishbone有点像AXI,只不过是开源的。Wishbone支持许多很棒的特点,如多master、流水线和块传输等。Wishbone总线空间的一部份还映射到了一个名为“配置和状态寄存器”(ConfigurationandStatusRegister,CSR)的总线上。其实Wishbone是高性能总线,但它须要更多的插口逻辑,但是只在外设带宽匹配总线带宽时才会发挥最佳性能。CSR有区域效应,从硬件和软件API两方面都可以适应任意寄存器显存,但性能较低。为此,CSR最适宜用作低速到中速的输入输出任务(比如命名配置和状态寄存器),这种任务中Wishbone特别适宜映射到显存上的I/O,这样可以提升带宽并改善延后,足以补偿区域效应带来的额外开支。

![图片[6]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_12.png)

在设计过程中,绝大多数外设的第一步都是映射到CSR空间,之后升级成显存映射实现,因而达到性能要求。因而,Precursor上的绝大部份外设都是仅支持CSR的设备,这并非碰巧。下边是每位CSR外设的简单介绍。须要提醒一点,你可以查看我们的参考指南以获取更详尽的信息。

![图片[7]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_14.png)

不仅CSR的I/O之外,还有一些I/O设备也映射到了显存,以实现高性能:

加密区域

后面描述的所有功能仅占用了FPGA大概20%的逻辑,而Precursor的FPGA的主要逻辑坐落加密区域。

![图片[8]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_16.gif)

![图片[9]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_17.png)

上图展示了在Precursor系统芯片设计中各个功能的相对规格。一些块(如半冗余SHA-512和SHA-2加速器)的存在,仅仅是由于FPGA中才能容纳那些功能,而不是由于有需求。辛运的是,删掉SHA-2块很简单,只须要注释掉4行代码,能节省大概2800个SLICELUT,相当于大概9%的设备资源。LiteX和svd2rust脚本会负责其余的一切!

![图片[10]-基于某个高度集成的芯片称为“系统芯片”(SystemonaChip)-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/07/1658401468233_18.png)

下边是加密区域中各个块的简略说明:

分块的思路

以上就是对Precursor系统芯片的介绍!我们根据功能和安全性分块,希望开发社区才能添加更多内容。只须要注释掉一些代码,就可以去除不须要的块,为你自己的创作腾出空间。Precursor的代码完全开源,没有任何隐藏的测试逻辑,也没有微代码块,你若果想追踪从电源键按下到第一条指令执行之间发生了哪些事情,也不须要签订保密合同。据悉,Precursor系统芯片还有一个值得你信赖的缘由:没有“暗物质”,设计完全透明。

原文:

暂无评论内容