Verilog 实例数组

对于一个定义明确的简单模块,比如加法器,如果我们要实例化它几十次上百次,而这些实例化的形式基本相同,那我们肯定不能单独配对。它是实例化的,此时我们可以使用一种方式来实例化一个数组,以便快速实例化。

例如,如果我们要实现的功能如下:

Now that you know how to build a full adder, make 3 instances of it to create a 3-bit binary ripple-carry adder. The adder adds two 3-bit numbers and a carry-in to produce a 3-bit sum and carry out. To encourage you to actually instantiate full adders, also output the carry-out from each full adder in the ripple-carry adder. cout[2] is the final carry-out from the last full adder, and is the carry-out you usually see.

给定的端口定义如下

![图片[1]-Verilog实例数组对于一个定义好的简单module,例如加法器-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/06/1656015038779_0.jpg)

module Adder3(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

![图片[2]-Verilog实例数组对于一个定义好的简单module,例如加法器-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/06/1656015038779_1.png)

那么我们可以先定义一个带进位的加法模块

module Adder1(

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule

![图片[3]-Verilog实例数组对于一个定义好的简单module,例如加法器-唐朝资源网](https://images.43s.cn/wp-content/uploads//2022/06/1656015038779_2.jpg)

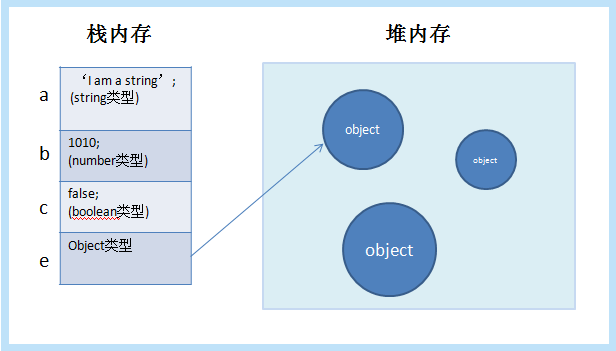

然后使用实例化数组语法

module Adder3(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

Adder1 Adder1[2:0](//将我们例化的模块写成一个一位加法器的三倍位宽

.a(a),//每一个端口的位宽都是原来一位加法器的三倍位宽

.b(b),

.cin({cout[1:0],cin}),

.cout(cout),

.sum(sum)

);

上面的实例化实际上实例化了三个add模块,分别命名为add_3[0]、add_3[1]、add_3[2];

从示意图中可以看出,确实实例化了三个Adder1模块。

© 版权声明

本站下载的源码均来自公开网络收集转发二次开发而来,

若侵犯了您的合法权益,请来信通知我们1413333033@qq.com,

我们会及时删除,给您带来的不便,我们深表歉意。

下载用户仅供学习交流,若使用商业用途,请购买正版授权,否则产生的一切后果将由下载用户自行承担,访问及下载者下载默认同意本站声明的免责申明,请合理使用切勿商用。

THE END

![[原] KVM 环境下MySQL性能对比-唐朝资源网](https://images.43s.cn/wp-content/uploads/2022/06/36b6cab091cb.webp)

暂无评论内容